Page History

...

The paragraph order in this page is intentional. They represent the steps you normally do when you want to port the Renesas BSP, i.e. you absolutely want to start from Flash Writer. When you get your first custom board samples the non-volatile memories are virgin and the first goals is to program them with bootloaders. One of the first thing you need to do is to adjust the DDR configuration to your own. Debugging DDR may be tricky but have it working is a major step toward success. You can test the DDR using some hidden Flash Writer commands. After that you may need to change the SPI configuration.

...

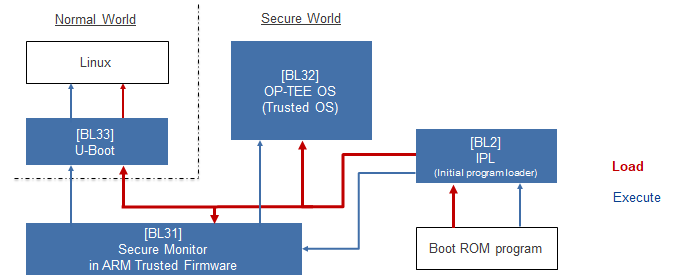

You do not normally need to modify many things in ATF and in any case only what is in the "plat/renesas/rz" folder. One of the first things ATF BL2 does is to configure the DDR. You would need to use the same (working) configuration used with Flash Writer, so there should be no surprise here, if the DDR works with Flash Writer then it will work with ATF as well.

-------------------------------

Then ATF loads BL31(image id=3), BL32 (again optionally, image id=4) and BL33 (u-boot, image id=5) from either QSPI or eMMC. Assuming everything goes fine u-boot prompt is finally reachable. The table below summarizes where the different actors in the boot process are typically stored and executed from.

...

Finally you can use Yocto to generate the root file system including all the bits and bobs you need to run your custom application.

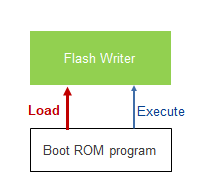

Flash Writer

Arm Trusted Firmware

u-boot

Linux Kernel

Yocto

Ubuntu

OpenWRT

Debian

- RZ-G /RZ-G2 BSP Porting Debian

Memory Map

- This section explains how DDR Memory is divided and configured.

- RZ-G/RZ-G2_BSP_MemoryMap

Changing Console Port

You can make use of the following changes to change console port from SCIF0 to SCIF2 in RZ/G2L-LC and RZ/V2L (Not applicable for RZ/G2UL). Please note that it NOT RECOMMENDED by Renesas to do so and is described here only for experimental purpose.

...

| Expand | ||

|---|---|---|

| ||

Trusted Firmware-A File: plat/renesas/rz/common/include/rzg2l_def.h #define RZG2L_SCIF0_BASE (0x1004B800) +#define RZG2L_SCIF2_BASE (0x1004C000) File: plat/renesas/rz/common/bl2_plat_setup.c initialize console driver */ ret = console_rzg2l_register( - RZG2L_SCIF0_BASE, + RZG2L_SCIF2_BASE, RZG2L_UART_INCK_HZ, RZG2L_UART_BARDRATE, &rzg2l_bl31_console); File: plat/renesas/rz/common/bl31_plat_setup.c initialize console driver */ ret = console_rzg2l_register( - RZG2L_SCIF0_BASE, + RZG2L_SCIF2_BASE, RZG2L_UART_INCK_HZ, RZG2L_UART_BARDRATE, &rzg2l_bl31_console); File: plat/renesas/rz/common/drivers/cpg.c { /* SCIF */

(uintptr_t)CPG_CLKON_SCIF,

(uintptr_t)CPG_CLKMON_SCIF,

- 0x001f0001,

+ 0x001f0004,

CPG_T_CLK

},

File: plat/renesas/rz/common/include/pfc_regs.h -#define PFC_MUX_TBL_NUM (4) +#define PFC_MUX_TBL_NUM (5) File: plat/renesas/rz/common/drivers/pfc.c { PFC_OFF, (uintptr_t)NULL, 0 } /* IEN */

+},

+/* P40(scif2) */

+{

+ { PFC_ON, (uintptr_t)PFC_PMC40, 0x1F }, /* PMC */

+ { PFC_ON, (uintptr_t)PFC_PFC40, 0x00011111 }, /* PFC */

+ { PFC_OFF, (uintptr_t)PFC_IOLH40, 0x0000000101010101 }, /* IOLH */

+ { PFC_OFF, (uintptr_t)PFC_PUPD40, 0x0000000000000000 }, /* PUPD */

+ { PFC_OFF, (uintptr_t)PFC_SR40, 0x0000000101010101 }, /* SR */

+ { PFC_OFF, (uintptr_t)NULL, 0 } /* IEN */

}

#endif

};

u-boot File: arch/arm/dts/smarc-rzg2l.dts aliases {

serial0 = &scif0;

+ serial1 = &scif2;

spi0 = &spibsc;

};

chosen {

- stdout-path = "serial0:115200n8";

+ stdout-path = "serial1:115200n8";

};

kernel File: arch/arm64/boot/dts/renesas/rzg2l-smarc.dtsi /* comment the #define statement to disable SCIF2 (SER0) on PMOD1 (CN7) */ -//#define PMOD1_SER0 1 +#define PMOD1_SER0 1 File: arch/arm64/boot/dts/renesas/rz-smarc-common.dtsi chosen {

- stdout-path = "serial0:115200n8";

+ stdout-path = "serial1:115200n8";

+ bootargs = "ignore_loglevel rw root=/dev/nfs ip=on";

};

File: drivers/clk/renesas/r9a07g044-cpg.c static const unsigned int r9a07g044_crit_mod_clks[] __initconst = {

MOD_CLK_BASE + R9A07G044_IA55_PCLK,

MOD_CLK_BASE + R9A07G044_IA55_CLK,

MOD_CLK_BASE + R9A07G044_DMAC_ACLK,

+ MOD_CLK_BASE + R9A07G044_SCIF2_CLK_PCK,

}; |

...