Page History

...

Prerequisites

A compatible JTAG hardware debugger device is required. Different JTAG devices can have slightly different procedure.

As an example, following guidance is for:

- Segger J-Link Debug Probe

- J-Link Website

- J-Link BASE, J-Link PLUS, J-Link PRO

- Requires 20-to-10 pin adapter

- Flyswatter2 device from Tin Can Tools, LLC.

- J-Link debug probes

- ARM-JTAG-20-10 Adapter (Mouser) ()

Environment

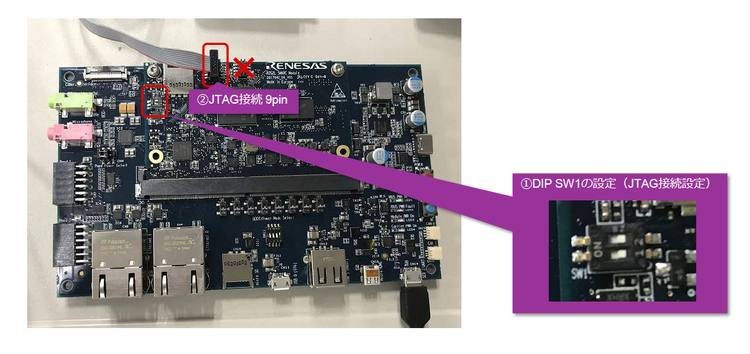

Below illustration shows how user should connect RZ/G2 platform with JTAG debugger and OpenOCD (run on a Linux Host PC). Note that most RZ/G2 development board has 10 pin JTAG header, so a JTAG converter (20pin-10pin) is required, for example the Olimex ARM-JTAG-20-10. The following pictures illustrates how to setup the environment with a Flyswatter2 and a EK874 (RZ/G2E) board. The setup is similar if other JTAG debuggers and/or devices are used.

Hardware setup

- Tigard Open Source Tool

- https://github.com/tigard-tools/tigard

- https://www.crowdsupply.com/securinghw/tigard

- Includes correct 10-pin JTAG cable (no adapter is needed)

- Requires USB-C cable for power and data (not included)

- 🛒 ($49) https://www.mouser.com/ProductDetail/Securing-Hardware/TIGARD-V1?qs=aP1CjGhiNiFnjSEE%2FnXyEw%3D%3D

- 🛒 ($49) https://1bitsquared.com/products/tigard

Hardware setup

Most RZ development boards has 10 pin JTAG header, so a JTAG converter (20pin-10pin) might be required depending on what JTAG adapter you are using. For example the Olimex ARM-JTAG-20-10. can be used to convert from 20-pin to 10-pin.

After connecting the devices as per guide in the previous section, follow below After connecting the devices as per guide in the previous section, follow below instructions to use OpenOCD and JTAG debugger. You must change the switches setting on development board to enable the JTAG debugging feature. The switches setting may be different for each development board. Please refer to the relevant board manual or user guide for detailed information.

...

Change switches as per below.

- SW1: OFF - OFF

...

Change switches as per below. Note that board version 3 (Rev C) or later must be used.

- SW12: change bit 4 and 5 to OFF to enable JTAG

- SW50: change to (2-3) side

- SW51: change to (1-2) side

...

Change switches as per below. Note that board rev. 3 or later must be used.

- SW1003: change bit 4 to OFF to enable JTAG

- SW305: change to (2-3) side

- SW2405: change to (1-2) side

Tigard Switch Setting

If you are using a Tigard, set the TARGET switch to 1v8

and the MODE switch to JTAG

Download and Build OpenOCD

To build OpenOCD you can use this script found in the https://github.com/renesas-rz/rzg_openocd repository.

$ wget https://raw.githubusercontent.com/renesas-rz/rzg_openocd/master/build_openocd .sh

$ wget https://raw.githubusercontent.com/renesas-rz/rzg_openocd/master/00020001-tcl-target-aarch64-Write-Memory-function-fix-for-self-mo.patch $ chmod +x ./build_openocd /* Avoid GIT error: server certificate verification failed */ $ export GIT_SSL_NO_VERIFY=1 $ ./build_openocd

Or manually follow the steps in that script:

...

renesas_rz_g2-Rename-to-renesas_rz-and-ad.patch

$ wget https://raw.githubusercontent.com/renesas-rz/rzg_openocd/master/0002-target-aarch64-MRS-MSR-support-for-system-register-a.patch

$ wget https://raw.githubusercontent.com/renesas-rz/rzg_openocd

...

The OpenOCD binaries can be found in the openocd/installdir/bin directory.

In the configuration, options that are commonly needed are --enable-ftdi to ensure ftdi related function (which Flyswatter2 uses) will be built. Same for J-Link, with --enable-jlink, however both should be recognized and added automatically during the configuration phase.

Note - The patch is not strictly needed. It slows down the download operations but it is required if an existing code in memory has to be replaced by using the JTAG.

Run OpenOCD

OpenOCD provides many setting scripts for many JTAG debugger and development boards under directory share/openocd/scripts/. Normally two suitable scripts has to be chosen, one for Debugger configuration and one for the development board or chip.

To debug with Flyswatter2 the following scripts is available:

interface/ftdi/flyswatter2.cfg

To debug with J-Link, instead:

interface/jlink.cfg

Then for the RZ/G2 family:

target/renesas_rz_g2.cfg

Finally different commands have to be used to select different devices belonging to the RZ/G2 family:

- SMARC RZ/G2L board: set SOC G2L (default), i.e. -c can be omitted

- SMARC RZ/G2LC board: set SOC G2LC

- SMARC RZ/G2UL board: set SOC G2UL

- EK874 RZ/G2E board: set SOC G2E

- HiHope RZ/G2M board: set SOC G2M

- HiHope RZ/G2N board: set SOC G2N

- HiHope RZ/G2H board: set SOC G2H

So, for example to run OpenOCD and attach to a RZ/G2L device using a Flyswatter 2 JTAG adapter:

...

/master/0003-target-aarch64-enable-disable-mmu-new-commands.patch

$ wget https://raw.githubusercontent.com/renesas-rz/rzg_openocd/master/0004-target-aarch64-Add-code-to-invaldate-the-instruction.patch

$ wget https://raw.githubusercontent.com/renesas-rz/rzg_openocd/master/0005-tcl-target-renesas_rz-add-hwthread-and-coreid.patch

$ chmod +x ./build_openocd.sh

$ export GIT_SSL_NO_VERIFY=1 # Avoid GIT error: server certificate verification failed

$ ./build_openocd.sh

Or manually follow the steps in that script:

The OpenOCD binaries can be found in the openocd/installdir/bin directory.

In the configuration, options that are commonly needed are --enable-ftdi to ensure ftdi related function will be built. Same for J-Link, with --enable-jlink, however both should be recognized and added automatically during the configuration phase.

Note - The patch is not strictly needed. It slows down the download operations but it is required if an existing code in memory has to be replaced by using the JTAG.

Run OpenOCD

OpenOCD provides many setting scripts for many JTAG debugger and development boards under directory share/openocd/scripts/.

Normally two suitable scripts has to be chosen, one for Debugger Configuration and one for the Development Board or SoC Configuration.

Debugger Configuration File

- To debug with J-Link, the following script is available: share/openocd/scripts/interface/jlink.cfg

- To debug with Tigard, the following script is available: share/openocd/scripts/interface/ftdi/

...

- tigard.cfg

Development Board or SoC Configuration File

- The Device configuration file for the RZ family is share/openocd/scripts/target/renesas_rz

...

- .cfg

...

In case of RZ/Five:

$ cd installdir

$ sudo bin/openocd -f share/openocd/scripts/interface/ftdi/flyswatter2.cfg -f share/openocd/scripts/target/renesas_rz_five.cfg

Please note that there's a way to avoid the usage of sudo by making sure that both the user and the debugger devices used belong to the dialout/plugdev groups.

You can modify the renesas_rz_*.cfg configure file to tweak the clock speed (default 4MHz), for example to increase it to 15MHz:

adapter speed 15000If openocd command succeeds, a message like these below appears:

Open On-Chip Debugger 0.11.0+dev-00182-gbd1569d1b-dirty (2021-05-25-10:23)

Licensed under GNU GPL v2

For bug reports, read

http://openocd.org/doc/doxygen/bugs.html

G2L

G2L - 0 CA57(s), 2 CA55(s), 0 CA53(s), 0 CR7(s), 1 CM33(s)

Boot Core - CA55

r9a07g044l.cpu

SMP targets: r9a07g044l.a55.0 r9a07g044l.a55.1

init_reset

Info : Listening on port 6666 for tcl connections

Info : Listening on port 4444 for telnet connections

Info : J-Link Lite V9 compiled May 17 2019 10:18:57

Info : Hardware version: 9.00

Info : VTarget = 1.833 V

Info : clock speed 4000 kHz

Info : JTAG tap: r9a07g044l.cpu tap/device found: 0x6ba00477 (mfg: 0x23b (ARM Ltd), part: 0xba00, ver: 0x6)

Info : DAP transaction stalled (WAIT) - slowing down

Info : DAP transaction stalled during replay (WAIT) - resending

Info : DAP transaction stalled (WAIT) - slowing down

Info : r9a07g044l.a55.0: hardware has 6 breakpoints, 4 watchpoints

Info : DAP transaction stalled (WAIT) - slowing down

Info : DAP transaction stalled during replay (WAIT) - resending

Info : r9a07g044l.a55.0 cluster 0 core 0 multi core

Info : starting gdb server for r9a07g044l.a55.0 on 3333

Info : Listening on port 3333 for gdb connections

Info : starting gdb server for r9a07g044l.m33 on 3334

Info : Listening on port 3334 for gdb connections

Info : gdb port disabled

Open On-Chip Debugger 0.11.0+dev-00663-gd1e14abdb-dirty (2022-05-10-07:54) Licensed under GNU GPL v2 For bug reports, read http://openocd.org/doc/doxygen/bugs.html r9A07g043u.cpu Info : Listening on port 6666 for tcl connections Info : Listening on port 4444 for telnet connections Info : J-Link Lite V9 compiled Feb 2 2021 16:32:48 Info : Hardware version: 9.00 Info : VTarget = 1.819 V Info : clock speed 4000 kHz Info : JTAG tap: r9A07g043u.cpu tap/device found: 0x1000563d (mfg: 0x31e (Andes Technology Corporation), part: 0x0005, ver: 0x1) Info : datacount=4 progbufsize=8 Info : Examined RISC-V core; found 1 harts Info : hart 0: XLEN=64, misa=0x800000000094312d Info : starting gdb server for r9A07g043u.cpu on 3333 Info : Listening on port 3333 for gdb connections

Note that the "DAP transaction stalled" messages are normal and do not affect the functionality.

Start debugging

Now that openocd command has succeeded, you can use GDB on your Linux Host PC and attach to GDB Server created by OpenOCD. Note that on the Linux machine there might be several instances of GDB, including the native GDB (x86_64). In order to debug the Cortex-A55 the Arm AArch64 cross GDB has to be used, normally the one included in the SDK generated by Yocto, target: aarch64-poky-linux. For the Cortex-M33, instead the target has to be arm-none-eabi (to be installed separately).

- Note: In the Official OpenOCD repository, the file name is renesas_rz_g2.cfg. However, in the patches you downloaded and ran, we renamed it to renesas_rz.cfg. We plan to mainline this change back into the official openocd repository eventually

Development Board or SoC Configuration (SoC selection)

Different commands have to be used to select different devices belonging to the RZ family:

- SMARC RZ/G2L board: "set SOC G2L" (default), i.e. -c can be omitted

- SMARC RZ/G2LC board: "set SOC G2LC"

- SMARC RZ/G2UL board: "set SOC G2UL"

- SMARC RZ/V2L board: "set SOC V2L"

- SMARC II RZ/G3S board: "set SOC G3S"

- EK874 RZ/G2E board: "set SOC G2E"

- HiHope RZ/G2M board: "set SOC G2M"

- HiHope RZ/G2N board: "set SOC G2N"

- HiHope RZ/G2H board: "set SOC G2H"

Example Command Lines:

Example to run OpenOCD and attach to a RZ/G2L device using a Segger J-Link JTAG adapter:

$ cd installdir

$ sudo bin/openocd -f share/openocd/scripts/interface/jlink.cfg -c "set SOC G2L" -f share/openocd/scripts/target/renesas_rz.cfg

Example to run OpenOCD and attach to a RZ/G2L device using a Tigard JTAG adapter:

$ cd installdir

$ sudo bin/openocd -f share/openocd/scripts/interface/ftdi/tigard.cfg -c "set SOC G2L" -f share/openocd/scripts/target/renesas_rz.cfg

RZ/Five uses a different configuration file (renesas_rz_five.cfg)

Example to run OpenOCD and attach to a RZ/Five device using a Segger J-LinkJTAG adapter:

$ cd installdir

$ sudo bin/openocd -f share/openocd/scripts/interface/jlink.cfg -f share/openocd/scripts/target/renesas_rz_five.cfg

Please note that there's a way to avoid the usage of sudo by making sure that both the user and the debugger devices used belong to the dialout/plugdev groups.

JTAG Adapter Clock Speed

You can modify the renesas_rz_*.cfg configure file to tweak the clock speed (default 4MHz), for example to increase it to 15MHz:

adapter speed 15000Verify Connection

If openocd command succeeds, a message like these below appears:

Open On-Chip Debugger 0.12.0+dev-01565-g5622ada82 (2024-04-10-13:59) Licensed under GNU GPL v2 For bug reports, read http://openocd.org/doc/doxygen/bugs.html G2L G2L - 0 CA57(s), 2 CA55(s), 0 CA53(s), 0 CR7(s), 1 CM33(s) Boot Core - CA55 r9a07g044l.cpu SMP targets: r9a07g044l.a55.0 r9a07g044l.a55.1 init_reset Info : Listening on port 6666 for tcl connections Info : Listening on port 4444 for telnet connections Info : J-Link Lite V10 compiled Jan 30 2023 11:28:07 Info : Hardware version: 10.10 Info : VTarget = 1.761 V Info : clock speed 4000 kHz Info : JTAG tap: r9a07g044l.cpu tap/device found: 0x6ba00477 (mfg: 0x23b (ARM Ltd), part: 0xba00, ver: 0x6) Info : r9a07g044l.a55.0: hardware has 6 breakpoints, 4 watchpoints Info : r9a07g044l.a55.0 cluster 0 core 0 multi core

Info : [r9a07g044l.a55.0] Examination succeed

Info : [r9a07g044l.axi_ap] Examination succeed Info : starting gdb server for r9a07g044l.a55.0 on 3333 Info : Listening on port 3333 for gdb connections Info : starting gdb server for r9a07g044l.m33 on 3334 Info : Listening on port 3334 for gdb connections Info : gdb port disabled

Open On-Chip Debugger 0.11.0+dev-00663-gd1e14abdb-dirty (2022-05-10-07:54)

Licensed under GNU GPL v2

For bug reports, read

http://openocd.org/doc/doxygen/bugs.html

r9A07g043u.cpu Info :

Listening on port 6666 for tcl connections

Info : Listening on port 4444 for telnet connections

Info : J-Link Lite V9 compiled Feb 2 2021 16:32:48

Info : Hardware version: 9.00

Info : VTarget = 1.819 V

Info : clock speed 4000 kHz

Info : JTAG tap: r9A07g043u.cpu tap/device found: 0x1000563d (mfg: 0x31e (Andes Technology Corporation), part: 0x0005, ver: 0x1)

Info : datacount=4 progbufsize=8 Info : Examined RISC-V core; found 1 harts

Info : hart 0: XLEN=64, misa=0x800000000094312d

Info : starting gdb server for r9A07g043u.cpu on 3333

Info : Listening on port 3333 for gdb connections

Note that the "DAP transaction stalled" messages are normal and do not affect the functionality.

Start debugging

Now that openocd command has succeeded, you can use GDB on your Linux Host PC and attach to GDB Server created by OpenOCD. Note that on the Linux machine there might be several instances of GDB, including the native GDB (x86_64). In order to debug the Cortex-A55 the Arm AArch64 cross GDB has to be used, normally the one included in the SDK generated by Yocto, target: aarch64-poky-linux. For the Cortex-M33, instead the target has to be arm-none-eabi (to be installed separately).

$ source /opt/poky/3.1.5/environment-setup-aarch64-poky-linux

$ $GDB

GNU gdb (GDB) 9.1

Copyright (C) 2020 Free Software Foundation, Inc.

License GPLv3+: GNU GPL version 3 or later <http://gnu.org/licenses/gpl.html>

This is free software: you are free to change and redistribute it.

There is NO WARRANTY, to the extent permitted by law.

Type "show copying" and "show warranty" for details.

This GDB was configured as "--host=x86_64-pokysdk-linux '''--target=aarch64-poky-linux'''".

Type "show configuration" for configuration details.

For bug reporting instructions, please see:

<http://www.gnu.org/software/gdb/bugs/>.

Find the GDB manual and other documentation resources online at:

<http://www.gnu.org/software/gdb/documentation/>.

For help, type "help".

Type "apropos word" to search for commands related to "word".

Instead of the gdb included in the SDK and generated by Yocto, you can also install a newer Arm toolchain, for example Version 13.2.Rel1 and launch the corresponding gdb:

$ aarch64-none-linux-gnu-gdb

GNU gdb (Arm GNU Toolchain 13.2.rel1 (Build arm-13.7)) 13.2.90.20231008-git

Copyright (C) 2023$ source /opt/poky/3.1.5/environment-setup-aarch64-poky-linux $ $GDB GNU gdb (GDB) 9.1 Copyright (C) 2020 Free Software Foundation, Inc.

License GPLv3+: GNU GPL version 3 or later <http<http://gnu.org/licenses/gpl.html> html>

This is free software: you are free to change and redistribute it.

There is NO WARRANTY, to the extent permitted by law.

Type "show copying" and "show warranty" for details.

This GDB was configured as "--host=x86_64-pokysdkpc-linux-gnu '''--target=aarch64-pokynone-linux'''-gnu".

Type "show configuration" for configuration details.

For bug reporting instructions, please see: <http

<https://wwwbugs.gnu.org/software/gdb/bugslinaro.org/>.

Find the GDB manual and other documentation resources online at:

<http<http://www.gnu.org/software/gdb/documentation/>.

For help, type "help".

Type "apropos word" to search for commands related to "word".

(gdb)

In case of RISC-V there are different options, assuming the GDB that comes with Yocto SDK is used (riscv64-oe-linux-gdb):

...

For example, for a bare metal Hello World application with semihosting enabled, this simple gdb script can be used (manually rest the target first):

target remote localhost:3333

mon reset

mon r9a07g044l.a55.0 arp_examine 0

mon r9a07g044l.a55.0 arp_examine 1

mon halt

mon arm semihosting enable

set $pc = 0x12000

c

...